批發裝飾網、勾花網等冶金礦產產品的應用與優勢

在現代工業和建筑領域,金屬網類產品憑借其強度高、耐用性強和多功能性,廣泛應用于各個行業。其中,裝飾網、勾花網、床面網、不銹鋼網帶、輸送帶和鐵絲網等產品,作為冶金礦產的重要組成部分,在提升生產效率和安全性能方面發揮著關鍵作用。本文將詳細介紹這些產品的特點、應用場景以及選購建議,幫助用戶更好地理解和利用這些資源。

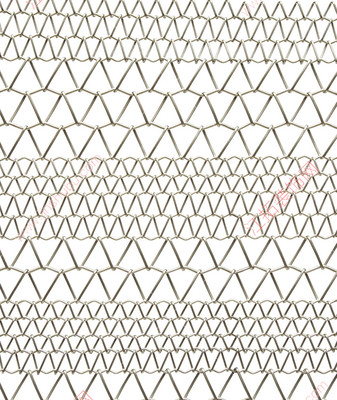

裝飾網主要用于建筑和室內裝飾,不僅具備美觀效果,還能增強結構的穩定性。它常被用于護欄、墻面覆蓋和吊頂設計,提供防護的同時,增添現代感。勾花網則以其柔韌性和高抗拉強度著稱,常用于邊坡防護、體育場圍欄和動物籠舍,有效防止土壤侵蝕和意外傷害。

床面網在工業設備中應用廣泛,例如用于篩分和過濾系統,能夠承受高負荷和頻繁振動,確保生產過程的連續性。不銹鋼網帶是自動化輸送系統的核心部件,適用于食品加工、化工和包裝行業,具有耐腐蝕、易清潔的優點,符合衛生標準。輸送帶則與網帶相輔相成,用于物料運輸,提高物流效率,減少人工成本。

鐵絲網作為傳統金屬網產品,用途多樣,從農業圍欄到建筑加固,都能看到它的身影。其成本低、安裝簡便的特點,使其成為大眾首選。

在選購這些產品時,用戶應考慮材質、網孔大小和承重能力等因素。例如,不銹鋼網帶適合潮濕環境,而鍍鋅鐵絲網則更適合戶外使用。通過世界工廠網等平臺,可以獲取詳細的產品信息和圖片,便于比較和批發采購。

這些冶金礦產產品不僅推動了工業發展,還為日常生活提供了便利。合理選擇和正確使用,將帶來更高的經濟效益和安全保障。

如若轉載,請注明出處:http://m.fvzfdhj.cn/product/11.html

更新時間:2026-04-18 22:06:10